## Overview Last lecture Review of D latches and flip-flops T flip-flops and SR latches State diagrams Asynchronous inputs Today Cascading flip-flops Clock skew Registers

CSE370, Lecture 17

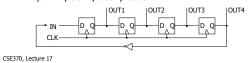

◆ Parallel-to-serial conversion for signal transmission

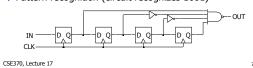

• Pattern recognition (circuit recognizes 1001)

## Counters

• Ring counter: Sequence is 1000, 0100, 0010, 0001 Assuming one of these patterns is the starting state

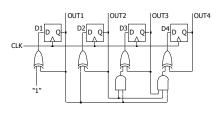

◆ Johnson counter: Sequence is 1000, 1100, 1110, 1111, 0111, 0011, 0001, 0000

## Class example: A binary counter

- ◆ Has logic between flip-flops

- Draw a timing diagram

CSE370, Lecture 17

## Summary: Sequential-logic building blocks

- Know latches and flip-flops

- R-S latch

- D latch and D flip-flop

- Master/slave flip-flops

- T flip-flop

- Know clocks, timing, timing diagrams

- Flip-flop timing and delay specifications

- Understand asynchronous inputs

- Metastability and how to avoid it

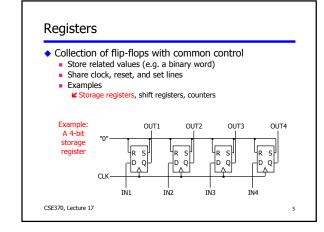

- Know basic registers

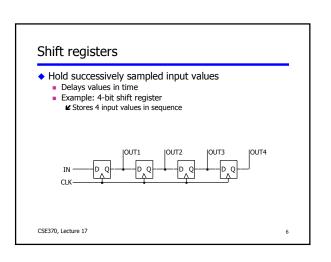

- Storage registers, shift registers, counters

CSE370, Lecture 17

10